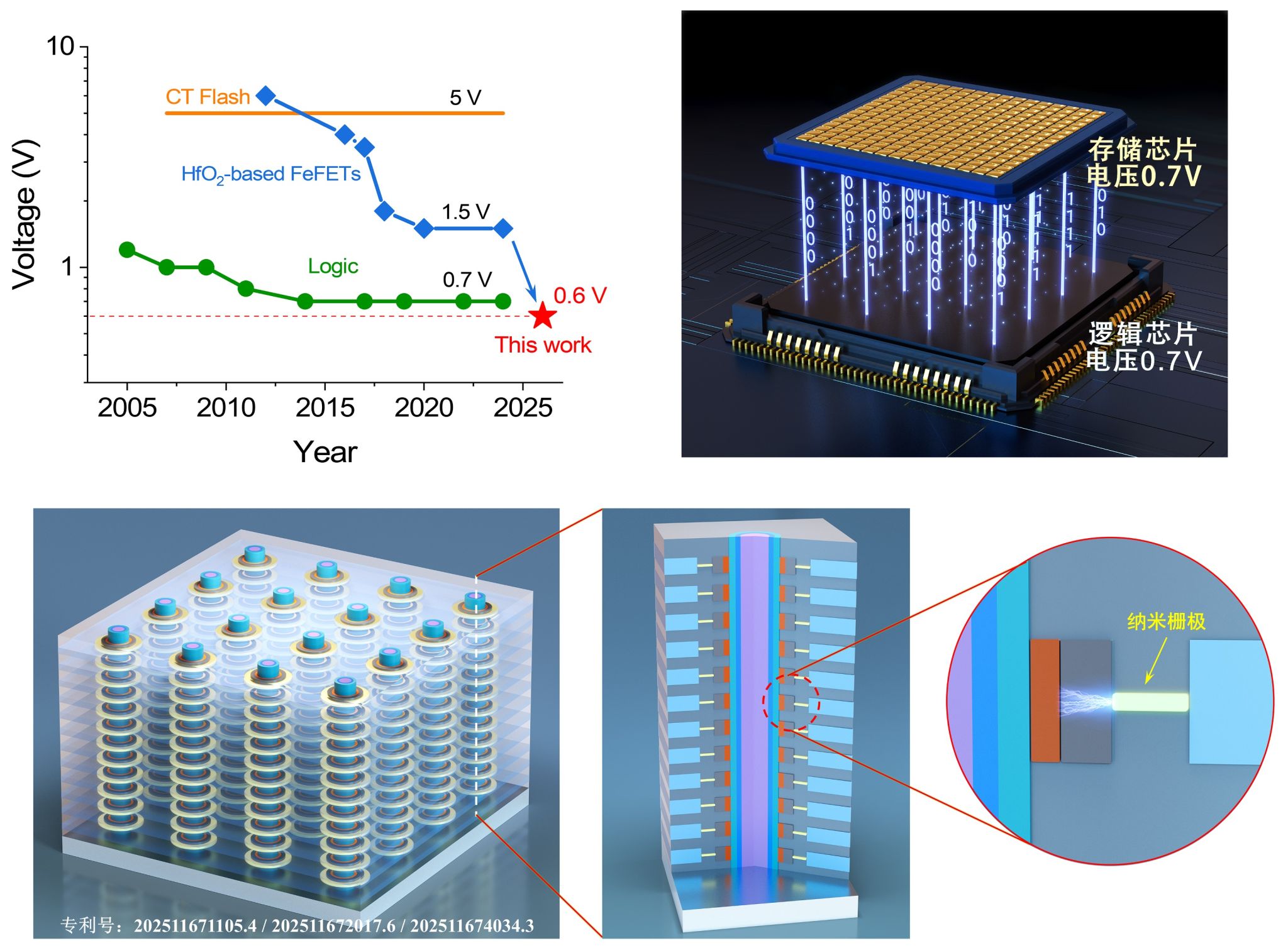

①北大团队成功研制出国际上尺寸最小、功耗最低的铁电晶体管,该器件可在0.6V超低电压下工作,能耗降低至0.45 fJ/μm,物理栅长缩减至1纳米极限; ②该研究利用纳米尺度场汇聚机理实现超低电压存储,打破了常规平板铁电体的矫顽电压极限,对构建更高效存储芯片有重要意义。

财联社2月24日讯,据北京大学电子学院官方消息,北京大学在非易失性存储器领域取得突破性进展。电子学院邱晨光-彭练矛团队成功将铁电晶体管物理栅长缩减至1纳米极限,创造性地制备了迄今尺寸最小、功耗最低的铁电晶体管,有望为AI芯片算力和能效提升提供核心器件支撑。相关研究成果在线发表于《科学·进展》上。

以下为文章原文:

电子学院邱晨光-彭练矛团队研制出国际上最低功耗铁电晶体管

北京大学在非易失性存储器领域取得突破性进展。电子学院邱晨光-彭练矛团队首次提出“纳米栅超低功耗铁电晶体管”。团队通过精巧设计铁电存储的器件结构,引入纳米栅极电场汇聚增强效应,研制出可在0.6V超低电压下工作的铁电晶体管,能耗降低至0.45 fJ/μm,并且将物理栅长缩减到1纳米极限,为国际上迄今尺寸最小、功耗最低的铁电晶体管,为构建高性能亚1纳米节点芯片和高算力AI芯片架构提供了更具潜力的新物理机制存储器件。该突破性成果以“Nanogate ferroelectric transistors with ultralow operation voltage of 0.6 V ”为题,在线发表于Science子刊《科学·进展》(Science Advances)。

逻辑器件和存储器件是构建集成电路的两大底层元器件。逻辑单元构成芯片的“运算与控制中枢”,存储单元构成芯片的“数据仓库”,两者占集成电路市场规模的70%以上。在摩尔定律的驱动下,逻辑晶体管通过制程微缩和架构迭代,性能不断提升,当前业界已实现2纳米节点逻辑芯片量产,并且CMOS晶体管在0.7V的低电压下工作。然而相比之下,非易失性存储器几十年来性能发展相对滞后,主流的非易失性Flash存储技术难以微缩到先进节点;最为关键的是,Flash存储需要在5V以上高电压下完成数据擦写。因此,现有芯片必须在逻辑单元和非易失存储之间集成升降压电路以完成工作电压转换,这带来了额外面积开销、能耗增加等一系列问题。更为重要的是,现代AI芯片架构的核心在于数据流优化,逻辑和存储之间的电压不匹配直接导致数据交互不畅通,严重拖累了AI芯片算力,并大幅增加了能耗。

铁电晶体管利用铁电材料的极化翻转实现数据存储,是后摩尔芯片技术中极具潜力的半导体存储器,受到学术界和业界广泛关注。凭借极化双稳态存储机制和三端晶体管结构,有望构建非易失性存算一体架构,实现存储与高速计算的完美结合,是破解“存储墙”和实现人工智能底层架构革新的关键新技术。然而迄今为止,受限于平板铁电体矫顽电压的物理限制,传统铁电晶体管仍需用1.5V以上电压实现铁电极化翻转和数据擦写。尽管优于Flash,但常规铁电晶体管理论上无法降低电压到0.7V以下,即无法匹配到逻辑电压水平。如何实现亚0.7V的超低电压存储技术,是突破存储墙瓶颈和提升AI芯片算力的关键。

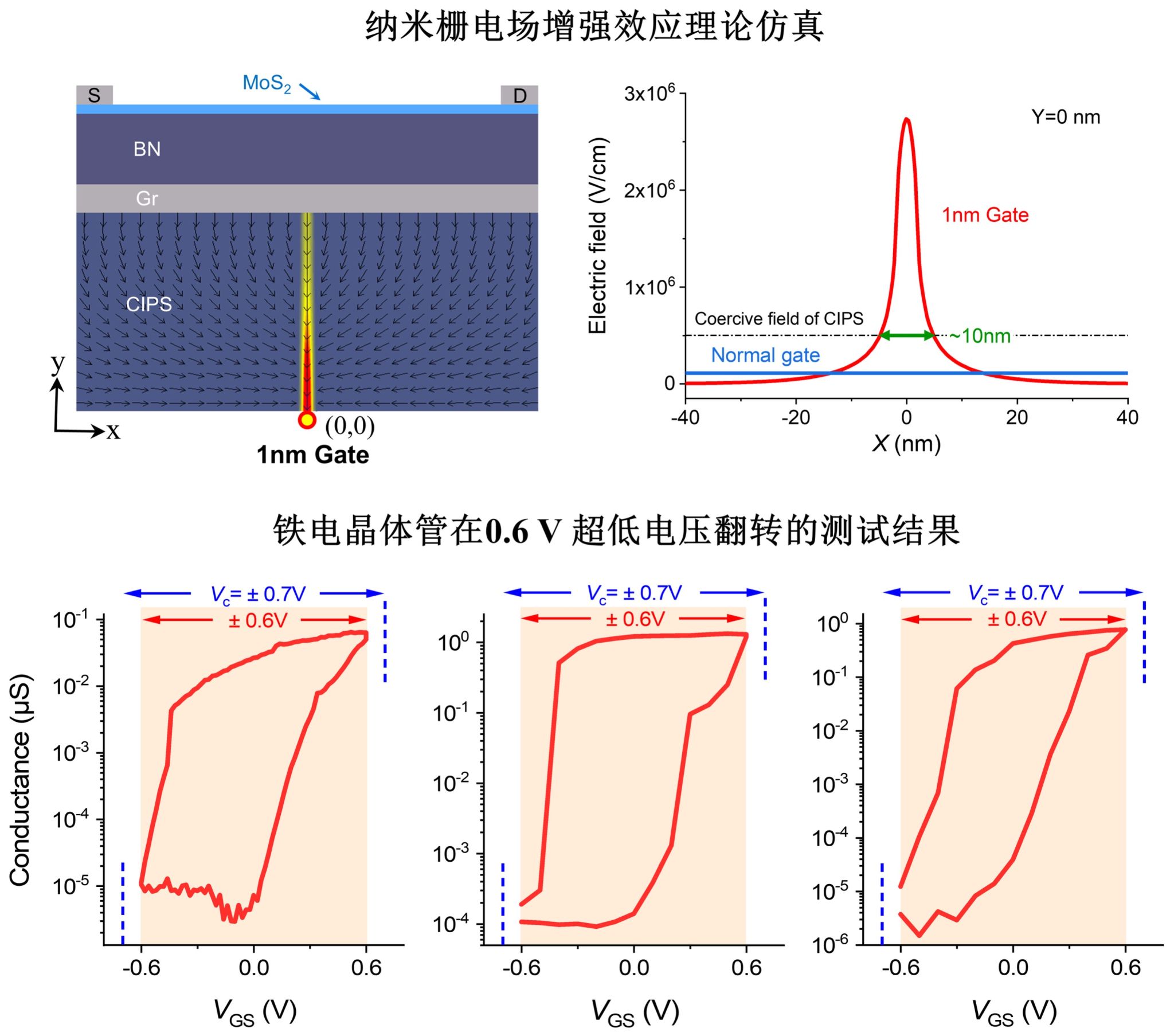

在本工作中,邱晨光-彭练矛团队首次提出“纳米栅铁电晶体管结构”和“纳米栅极电场增强机理”。通过优化器件结构,巧妙地将栅电极尺寸缩小到纳米极限尺度。利用纳米栅的尖端电场汇聚效应,在铁电层中构建了高度局域化的强电场汇聚区,有效地放大了局部电场强度,大幅降低铁电极化翻转电压,超越了常规平板铁电体的矫顽电压极限,打破了“低电压与高矫顽电场不可兼得”的固有认知,实现了0.6V超低工作电压,将铁电存储电压降低到和逻辑电压相当水平。研制的铁电晶体管能耗水平低至0.45 fJ/μm,领先国际已有报道一个数量级,存储速度接近1纳秒。该研究在国际上首次发现铁电晶体管具有反常的尺寸微缩优势,即物理栅长微缩到极限1纳米时显著汇聚并增强了电场,极小栅极尺寸有效改善了铁电存储特性,充分表明铁电存储器在构建未来亚纳米节点芯片具有显著优势。